LC78834M

Stereo 18-bit Digital Audio D/A Converter with On-Chip 4 fs Digital Filters

## Preliminary

## **Overview**

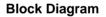

The LC78834M is a CMOS stereo 18-bit D/A converter LSI that includes  $4\times$  oversampling digital filters, output op amps, and analog filter op amps on chip.

## **Functions and Features**

- Digital filter block

- 4× oversampling filters: two-stage FIR filter structure (43rd order and 11th order)

- De-emphasis filters: support for fs = 32, 44.1, and 48 kHz

- Soft muting

- D/A converter block

- Dynamic level shifting 18-bit D/A converter

- Two D/A converter channels built in (in-phase outputs)

- Built-in output op amps

- Built-in analog filter op amps

- System clock: support for both 384 fs and 512 fs

- Single 5 V power supply

- Low voltage operation supported ( 3.5 V)

- Si gate CMOS process (low power)

## **Specifications**

## Absolute Maximum Ratings at $V_{SS} = 0 V$

#### Parameter Symbol Conditions Ratings Unit -0.3 to +7.0 V Maximum supply voltage V<sub>DD</sub> max V Input voltage -0.3 to V<sub>DD</sub> + 0.3 VIN -0.3 to V<sub>DD</sub> + 0.3 V Output voltage VOUT Operating temperature Topr -30 to +75 °C Storage temperature Tstg -40 to +125 °C

## **Allowable Operating Ranges**

| Parameter             | Symbol          | Conditions | min | typ | max | Unit |

|-----------------------|-----------------|------------|-----|-----|-----|------|

| Supply voltage        | V <sub>DD</sub> |            | 3.5 | 5.0 | 5.5 | V    |

| Operating temperature | Topr            |            | -30 |     | +75 | °C   |

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

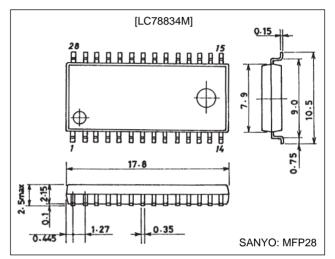

# Package Dimensions

unit: mm

3091-MFP28

| Parameter                    | Symbol            | Conditions                                                               |                     | Ratings |                     |      |

|------------------------------|-------------------|--------------------------------------------------------------------------|---------------------|---------|---------------------|------|

| Falameter                    | Symbol            | Conditions                                                               | min                 | typ     | max                 | Unit |

| Input high-level voltage (1) | V <sub>IH</sub> 1 | Pins 1, 2, 3, 4, 5, 6, 7, 8, 9, 15 and 16                                | 2.2                 |         |                     | V    |

| Input low-level voltage (1)  | V <sub>IL</sub> 1 | Pins 1, 2, 3, 4, 5, 6, 7, 8, 9, 15 and 16                                |                     |         | 0.8                 | V    |

| Input high-level voltage (2) | V <sub>IH</sub> 2 | Pin 13                                                                   | 0.7 V <sub>DD</sub> |         |                     | V    |

| Input low-level voltage (2)  | V <sub>IL</sub> 2 | Pin 13                                                                   |                     |         | 0.3 V <sub>DD</sub> | V    |

| Output high-level voltage    | V <sub>OH</sub>   | Pin 11, I <sub>OH</sub> = -3 mA                                          | 2.4                 |         |                     | V    |

| Output low-level voltage     | V <sub>OL</sub>   | Pin 11, I <sub>OL</sub> = 3 mA                                           |                     |         | 0.4                 | V    |

| Input leakage current        | VL                | Pins 1, 2, 3, 4, 5, 6, 7, 8, 9, 13, 15 and 16, $V_{I}$ = $V_{SS},V_{DD}$ | -25                 |         | +25                 | μA   |

# DC Characteristics at Ta = –30 to +75°C, $V_{DD}$ = 3.5 to 5.5 V, $V_{SS}$ = 0 V

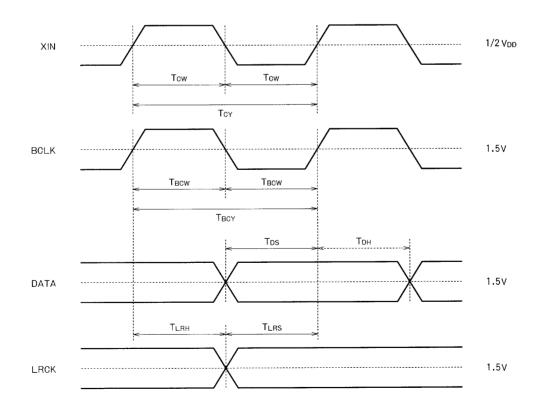

# AC Characteristics at Ta = –30 to +75°C, $V_{DD}$ = 3.5 to 5.5 V, $V_{SS}$ = 0 V

| Parameter            | Symbol           | Conditions                                            | Ratings |     |      | Unit |

|----------------------|------------------|-------------------------------------------------------|---------|-----|------|------|

| Falameter            | Symbol           | Conditions                                            | min     | typ | max  |      |

| Oscillator frequency | f <sub>X</sub>   | The XIN pin when a crystal oscillator is used         | 1.0     |     | 25   | MHz  |

| Clock pulse width    | t <sub>CW</sub>  | The XIN pin when an external clock signal is provided | 18      |     |      | ns   |

| Clock pulse period   | t <sub>CY</sub>  | The XIN pin when an external clock signal is provided | 40      |     | 1000 | ns   |

| BCLK pulse width     | t <sub>BCW</sub> |                                                       | 60      |     |      | ns   |

| BCLK pulse period    | t <sub>BCY</sub> |                                                       | 120     |     |      | ns   |

| Data setup time      | t <sub>DS</sub>  |                                                       | 40      |     |      | ns   |

| Data hold time       | t <sub>DH</sub>  |                                                       | 40      |     |      | ns   |

| LRCK setup time      | t <sub>LRS</sub> |                                                       | 40      |     |      | ns   |

| LRCK hold time       | t <sub>LRH</sub> |                                                       | 40      |     |      | ns   |

## Audio Input Waveforms

## Electrical Characteristics for D/A Converter (1) at Ta = $25^{\circ}$ C, AV<sub>DD</sub> = DV<sub>DD</sub> = 5.0 V, AGND = DGND = 0 V, unless otherwise specified

| Parameter                 | Symbol | /mbol Conditions   | Ratings |     |      | Unit |

|---------------------------|--------|--------------------|---------|-----|------|------|

|                           | Symbol | Condutoris         | min     | typ | max  |      |

| D/A converter resolution  | RES    |                    |         | 18  |      | Bits |

| Total harmonic distortion | THD    | 1 kHz, at 0 dB, *1 |         |     | 0.08 | %    |

| Dynamic range             | DR     | 1 kHz, at –60 dB   | 90      |     |      | dB   |

| Crosstalk                 | СТ     | 1 kHz, at 0 dB, *1 |         |     | -85  | dB   |

| Signal-to-noise ratio     | S/N    | JIS-A              | 96      |     |      | dB   |

| Full-scale output voltage | VFS    |                    | 2.2     | 2.4 | 2.6  | Vp-p |

| Power dissipation         | Pd     | 1 kHz, at 0 dB, *2 |         | 135 | 200  | mW   |

| Output load resistance    | RL     | Pins 21 and 23     | 5       |     |      | kΩ   |

## **Electrical Characteristics for D/A Converter (2)**

## at Ta = $25^{\circ}$ C, AV<sub>DD</sub> = DV<sub>DD</sub> = 3.5 V, AGND = DGND = 0 V, unless otherwise specified

| Parameter                 | Symbol | Conditions         | Ratings |     |      | Unit |

|---------------------------|--------|--------------------|---------|-----|------|------|

|                           | Symbol | Conditions         | min     | typ | max  | Onit |

| D/A converter resolution  | RES    |                    |         | 18  |      | Bits |

| Total harmonic distortion | THD    | 1 kHz, at 0 dB, *1 |         |     | 0.12 | %    |

| Dynamic range             | DR     | 1 kHz, at –60 dB   | 90      |     |      | dB   |

| Crosstalk                 | СТ     | 1 kHz, at 0 dB, *1 |         |     | -85  | dB   |

| Signal-to-noise ratio     | S/N    | JIS-A              | 96      |     |      | dB   |

| Full-scale output voltage | VFS    |                    | 1.5     | 1.7 | 1.9  | Vp-p |

| Power dissipation         | Pd     | 1 kHz, at 0 dB, *3 |         | 50  | 75   | mW   |

| Output load resistance    | RL     | Pins 21 and 23     | 15      |     |      | kΩ   |

Note: 1. "0 dB" means the full scale output level.

2. With the XIN pin (pin 13) at 1.5 to 3.5 V,  $f_X = 16.9344$  MHz, fs = 44.1 kHz (384 fs) 3. With the XIN pin (pin 13) at 1.0 to 2.5 V,  $f_X = 16.9344$  MHz, fs = 44.1 kHz (384 fs)

## **Operational Amplifier Block** at Ta = $25^{\circ}$ C, AV<sub>DD</sub> = DV<sub>DD</sub> = 5.0 V, AGND = DGND = 0 V, unless otherwise specified

| Parameter                       | Sumbol | Symbol Conditions -      | Ratings |     |     | Unit |

|---------------------------------|--------|--------------------------|---------|-----|-----|------|

|                                 | Symbol |                          | min     | typ | max |      |

| Slew rate                       | SR     | RL = 10 kΩ               |         | 9   |     | V/µs |

| Input offset voltage            | VIO    |                          |         | 1.5 |     | mV   |

| Gain-bandwidth product          | FT     | V <sub>IN</sub> = 2 Vp-p |         | 2.0 |     | MHz  |

| Maximum output voltage          | VOPP   | RL = 10 kΩ               | 0.3     |     | 4.7 | V    |

| Common-mode input voltage range | VIC    |                          | 0.6     |     | 3.6 | V    |

| Output load resistance          | RL     | Pins 18 and 26           | 5       |     |     | kΩ   |

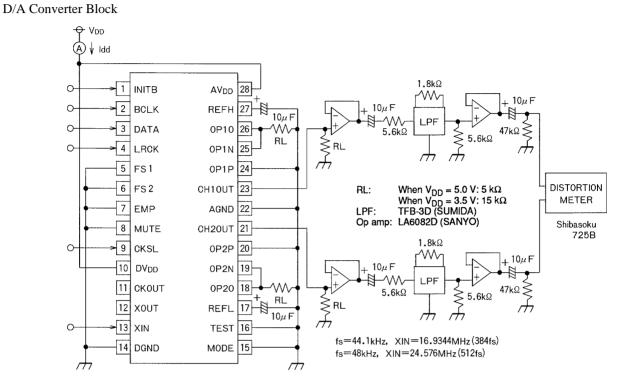

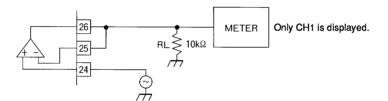

## **Test Circuits**

#### **Operational Amplifier Block**

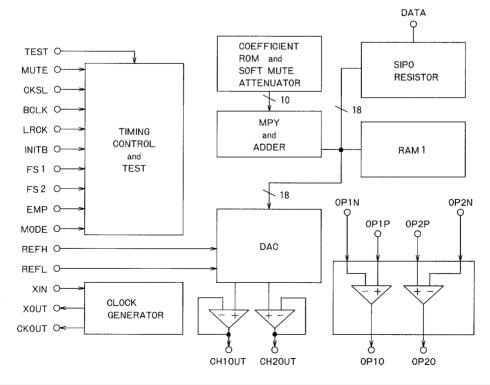

## Pin Assignment

## **Pin Functions**

| Pin No. | Symbol           | Function                                                                                                                                        |  |  |  |  |  |

|---------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1       | INITB            | Initialization signal input. The LC78834M is initialized on a low input.                                                                        |  |  |  |  |  |

| 2       | BCLK             | Bit clock input                                                                                                                                 |  |  |  |  |  |

| 3       | DATA             | Digital audio data input<br>Data is input in a two's complement MSB first format.                                                               |  |  |  |  |  |

| 4       | LRCK             | LR clock input<br>High: CH1 input; Low: CH2 input                                                                                               |  |  |  |  |  |

| 5       | FS1              | De-emphasis filter 32, 44.1, or 48 kHz mode selection                                                                                           |  |  |  |  |  |

|         |                  | FS1 L H H L                                                                                                                                     |  |  |  |  |  |

| 6       | FS2              | FS2 L H H   fs 44.1 kHz 32 kHz 48 kHz                                                                                                           |  |  |  |  |  |

| 7       | EMP              | De-emphasis filter on/off switching<br>High: on; Low: off.                                                                                      |  |  |  |  |  |

| 8       | MUTE             | Mute signal input<br>High: Soft muting on.                                                                                                      |  |  |  |  |  |

| 9       | CKSL             | System clock selection<br>High: 512 fs; Low: 384 fs                                                                                             |  |  |  |  |  |

| 10      | DV <sub>DD</sub> | Digital system power supply                                                                                                                     |  |  |  |  |  |

| 11      | CKOUT            | Clock output                                                                                                                                    |  |  |  |  |  |

| 12      | XOUT             | Crystal oscillator output (system clock output)                                                                                                 |  |  |  |  |  |

| 13      | XIN              | Crystal oscillator input (system clock input)                                                                                                   |  |  |  |  |  |

| 14      | DGND             | Digital system ground                                                                                                                           |  |  |  |  |  |

| 15      | MODE             | Digital audio data format selection<br>High: 18-bit data input<br>Low: 16-bit data input<br>See section 4., "Digital Audio Data Input", page 8. |  |  |  |  |  |

| 16      | TEST             | Test. Connect to DGND in normal operation.                                                                                                      |  |  |  |  |  |

| 17      | REFL             | Low-level reference voltage<br>Normally connected to AGND through a capacitor.                                                                  |  |  |  |  |  |

| 18      | OP2O             | Op amp 2 output                                                                                                                                 |  |  |  |  |  |

| 19      | OP2N             | Op amp 2 inverting input                                                                                                                        |  |  |  |  |  |

| 20      | OP2P             | Op amp 2 non-inverting input                                                                                                                    |  |  |  |  |  |

| 21      | CH2OUT           | CH2 analog output                                                                                                                               |  |  |  |  |  |

| 22      | AGND             | Analog system ground                                                                                                                            |  |  |  |  |  |

| 23      | CH1OUT           | CH1 analog output                                                                                                                               |  |  |  |  |  |

| 24      | OP1P             | Op amp 1 non-inverting input                                                                                                                    |  |  |  |  |  |

| 25      | OP1N             | Op amp 1 inverting input                                                                                                                        |  |  |  |  |  |

| 26      | OP10             | Op amp 1 output                                                                                                                                 |  |  |  |  |  |

| 27      | REFH             | High-level reference voltage<br>Normally connected to AGND through a capacitor.                                                                 |  |  |  |  |  |

| 28      | AV <sub>DD</sub> | Analog system ground                                                                                                                            |  |  |  |  |  |

## LC78834M Operation

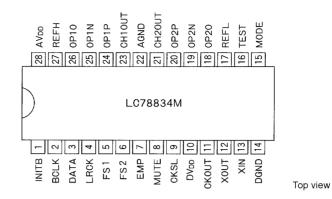

1. Digital Filters

The LC78834M performs the following processing.

• Oversampling

Two 2× interpolation filters (constructed as FIR filters) are cascade connected.

Two FIR filter stages, a 43rd order and an eleventh order, are cascade connected to perform 4× oversampling.

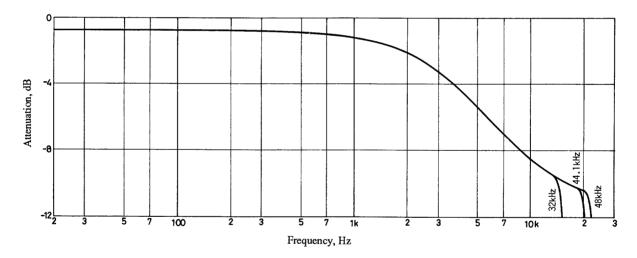

• De-emphasis

A first-order IIR filter is used for digital de-emphasis.

The filter coefficients are set up to correspond to the sampling frequency fs, which may be 32, 44.1, or 48 kHz. See page 11 for the filter characteristics when de-emphasis is on.

- De-emphasis on/off

- De-emphasis on: EMP pin = high De-emphasis off: EMP pin = low

- Filter coefficient selection

| FS1 | L        | Н | Н      | L      |

|-----|----------|---|--------|--------|

| FS2 | L        | L | н      | н      |

| fs  | 44.1 kHz |   | 32 kHz | 48 kHz |

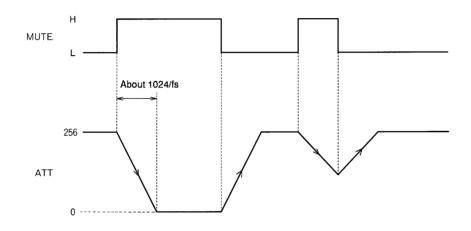

• Soft mute

The soft muting function uses the built-in digital attenuator. The following formula gives the attenuation.

20 · log (ATT/256) dB

The ATT parameter is an integer between 0 and 256. However, note that the attenuation will be  $-\infty$  when ATT is zero.

When the MUTE pin is set to the high level, one is subtracted from the ATT parameter repeatedly moving it towards zero thus changing the attenuation towards  $-\infty$ . Inversely, when the MUTE pin is set to the high level, one is added to the ATT parameter repeatedly moving it towards 256 thus changing the attenuation towards unity. The time required for the soft mute function to operate is about 1024/fs.

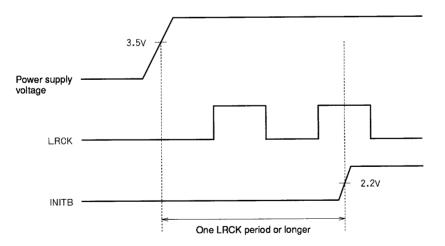

## 2. Initialization

The LC78834M must be initialized when power is first applied and when the system clock is switched. The LC78834M is initialized by setting the INITB pin to the low level. The required length of this initial low level period is defined as follows. Once the power supply has stabilized, input the XIN, BCLK and LRCK signals. The low level on the INITB pin must be held until at least one full cycle of the LRCK signal has completed, as shown in the figure.

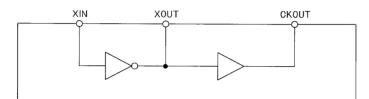

## 3. System Clock

The LC78834M can handle two system clocks types: either a 384 fs clock or a 512 fs clock. The CKSL pin selects which clock type is used.

| CKSL | System Clock |

|------|--------------|

| L    | 384 fs       |

| н    | 512 fs       |

## • CKOUT pin

The CKOUT pin is a system clock output pin.

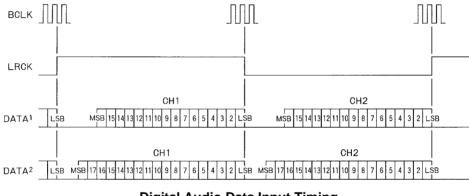

## 4. Digital Audio Data Input

Digital audio data is a 16- or 18-bit serial signal in a two's complement MSB first format. The 16- or 18-bit serial data is input from the DATA pin to an internal register on the rising edge of the BCLK signal, and that register is read in on the rising and falling edges of the LRCK signal.

## **Digital Audio Data Input Timing**

Note: When the MODE pin is low, DATA<sup>1</sup> is read in, and when high, DATA<sup>2</sup>.

## 5. D/A Converter Block

The LC78834M incorporates two independent 18-bit D/A converters, one each for channel 1 and channel 2, as well as two output op amps.

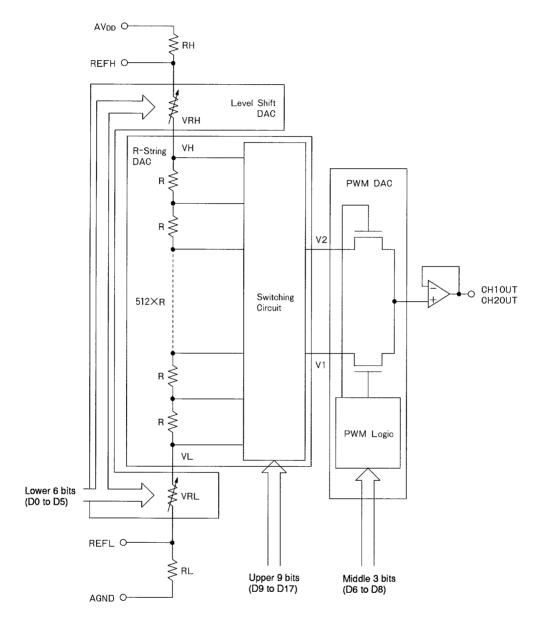

These D/A converters are based on a dynamic level shifting conversion scheme which combines resistor string D/A conversion (R-string DAC), PWM (pulse width modulation) D/A conversion (PWM DAC), and level shifting D/A conversion (level shift DAC) as shown in the figure.

## • R-string DAC

The R-string DAC is a 9-bit D/A converter that consists of  $512 (= 2^9)$  individual resistors (each with resistance R) connected in series that divide the voltage applied at the ends of that resistor string into 512 equal sections. Two adjacent potentials, V1 and V2, of the voltage divided potentials, are selected by a switching circuit according to the upper 9 bits of the data (D9 to D15). These two potentials are output to the PWM DAC. Note that V2 – V1 will be equal to (VH – VL)/512.

## • PWM DAC

The PWM DAC is a 3-bit D/A converter that divides the span of the two potentials V1 and V2 output from the Rstring DAC by eight. This circuit outputs one or the other of the two potentials V1 and V2 from the CH1OUT (or CH2OUT) pin depending on the value of the middle three bits (D6 to D8) of the data.

• Level-shift DAC

The level-shift DAC is a 6-bit D/A converter that consists of two variable resistors, VRH and VRL, inserted in series at the ends of the R-string DAC resistor string. The level-shift DAC controls the VRH and VRL variable resistors according to the lower six bits of the data (D0 to D5) as follows.

- The sum of the resistances of VRH and VRL is held constant for all values of the data.

- The values of VRH and VRL are set to be between 0 and 63 times R/512 according to the value of the data. (Here, R is the value of the resistance of the individual resistors in the R-string DAC.)

This changes the values of the R-string DAC outputs V1 and V2 in the range 0 to  $63 \times \Delta V/512$  (where  $\Delta V = (VH - VL)/512$ ) in steps of  $\Delta V/512$ .

• Reference resistors RH and RL

Capacitors (about 10  $\mu$ F) must be connected between REFH and AGND and between REFL and AGND. When AV<sub>DD</sub> = 5.0 V and AGND = 0 V, the LC78834M's maximum output amplitude should be set to be the range 1.3 to 3.7 V (2.4 Vp-p) for a 0 dB playback level by the resistors RH and RL.

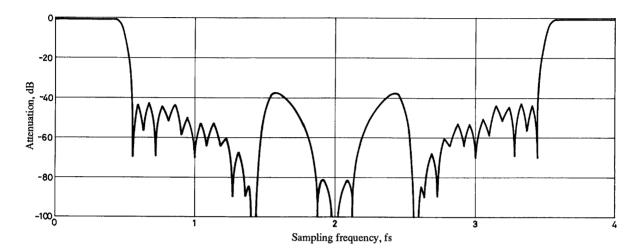

## **Filter Characteristics**

4× oversampling Ripple: Within ±0.05 dB Attenuation: Not more than -35 dB

1. De-emphasis

2. De-emphasis On Pass Band Characteristics

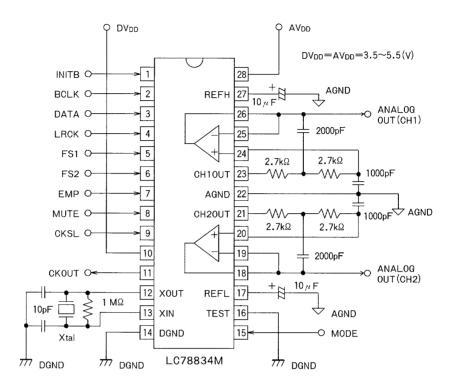

#### **Sample Application Circuit**

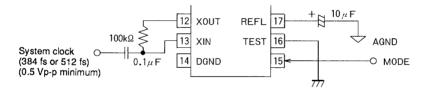

#### **External System Clock Supply Circuit**

- Notes: 1. The nodes marked DV<sub>DD</sub> and DGND must be connected to the digital system power supply, and the nodes marked AV<sub>DD</sub> and AGND must be connected to the analog system power supply.

- 2. TA low-impedance high-stability power supply (equivalent to a commercial three-terminal regulator) must be used for AV<sub>DD</sub>.

- 3. Since it is possible for latchup to occur if the pin 10 ( $DV_{DD}$ ) and the pin 28 ( $AV_{DD}$ ) power supply rise timings differ, the pin 10 and pin 28 power supply application circuit must be designed so that no time differential occurs.

- 4. After power is applied, the XIN pin clock signal must be provided promptly. If the XIN pin is held fixed (at low or high) after power is supplied, the IC may be destroyed.

## **Power Application Timing**

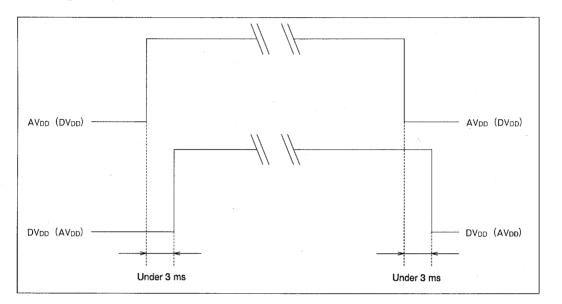

- 1. The analog power supply  $(AV_{DD})$  and the digital power supply  $(DV_{DD})$  must be brought up at the same time and must be turned off at the same time.

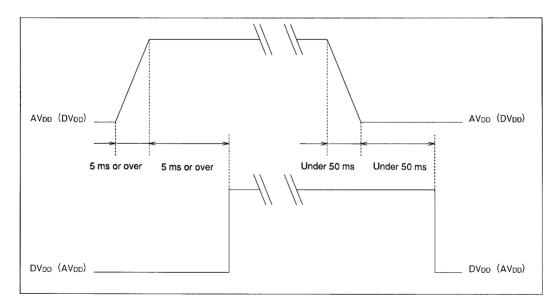

- 2. If a time difference occurs between the analog and digital power supplies, design the circuit to meet the following conditions.

- The power supply rise and fall times must be less than 3 ms apart as shown in Figure 1.

- If the time difference is over 3 ms, then allocate 5 ms or over as the rise or fall time of the power supply that rises or falls first respectively. Furthermore, the time difference must be under 50 ms.

Figure 1

Figure 2

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of September, 1998. Specifications and information herein are subject to change without notice.